# WELCOME TO Adda 2417

"If you can think, you can Achieve"

So start thinking..

Renu Raj Garg

M.Tech (VLSI Design)

13 Year of Teaching

Experience

Worked 10 Year in NTRO

# **GATE 2024**

# COMMUNICATION

TIME- 9:00PM

RENU SIR

**Chapter-2 Digital Communications**

In today's lecture we will cover the following Topis:

1. Questions from Base Band Data Communication

#### SUBSCRIBE NOW

#### Gate Adda247

YouTube Channel

Congratulations FROM ADDA 247 FAMILY

EE GAURAV MAHAJAN

# Know How You Can Ask Your Doubts 24x7.

Direct interaction with Adda247 Faculty team

AND THE RESIDENCE OF THE PARTY OF THE PARTY

No Subscription Required

Free

Start Apr 11, 2023

7:30 AM to 11:30 PM

# Ou Tune Classes Schedule (2)

| <b>EXAM TARGET</b>  | SUBJECT            | TIME     | FACULTY    |

|---------------------|--------------------|----------|------------|

| ALL PSUs            | ENGINEERING MATHS  | 11:00 AM | ANANT SIR  |

| <b>GATE 2024-25</b> | NETWORK THEORY     | 6:00 PM  | RAVISIR    |

| <b>GATE 2024-25</b> | ELECTRICAL MACHINE | 7:30 PM  | SANTAN SIR |

| GATE 2024-25        | COMMUNICATION      | 9:00 PM  | RENU SIR   |

# FREE APP CLASS SCHEDULE

#### EE & ECEENGINEERING

|   | NETWORK THEORY             | SATURDAY Live @11AM | RAVISIR      |

|---|----------------------------|---------------------|--------------|

|   | COMMUNICATION              | WEDNESDAY Live @8PM | RENU SIR     |

| _ | ANALOG<br>ELECTRONICS      | THURSDAY Live @8PM  | LAWRENCE SIR |

|   | ENGINEERING<br>MATHEMATICS | FRIDAY Live @11AM   | ANANT SIR    |

|   | ELECTRICAL<br>MACHINE      | MONDAY Live @8PM    | SANTAN SIR   |

# Adda[24]7

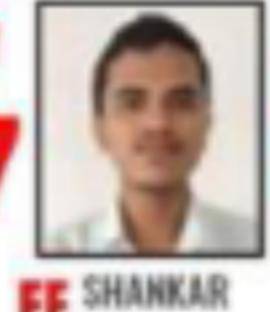

#### [IES-EC-2000]

A band – pass signal has significant frequency components in the range of 1.5 MHz to 2 MHz. If the signals to be reconstructed from its sample, the minimum sampling frequency will be

(B) 2MHz

(C) 3.5 MHz

(D) 4 MHz

we am Ha MR - ew = 4MHz

fiznr =)(fi)min = 4MHz

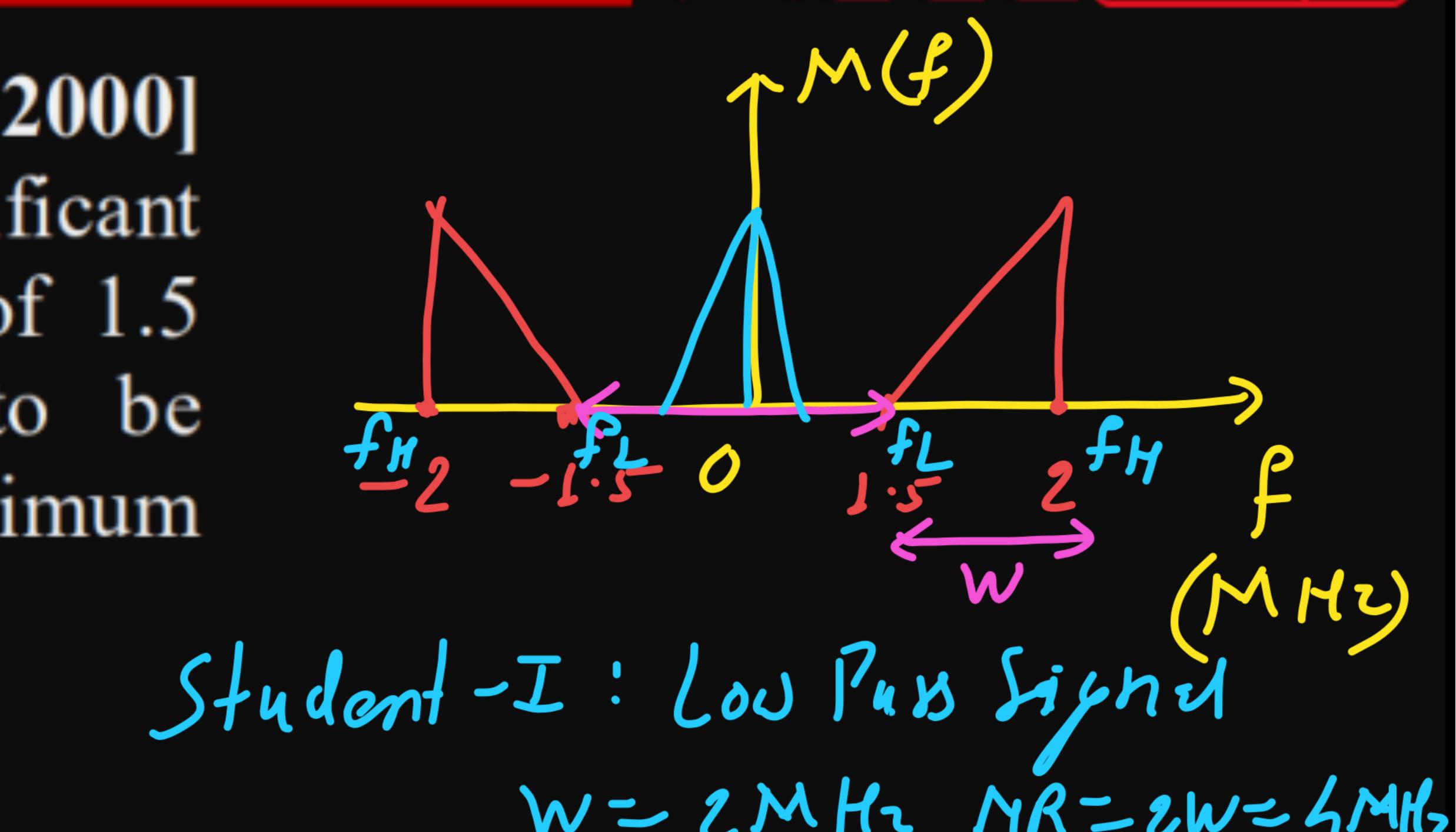

#### [IES – EC - 2010]

The spectrum of a band pass signal spans from 20 kHz to 30 kHz. The signal can be recovered ideally from the sampled values when the sampling rate is at least

$$\frac{2fL}{2W} = \frac{h^0}{2U} = 2 = m$$

$$\frac{2fH}{2W} = \frac{68}{2U} = 3 = m+1$$

$$\frac{2fL}{m} = \frac{4ox}{2} = 20KHz$$

$$\frac{2fH}{m+1} = \frac{6ok}{3} = 20KHz$$

CUIM

# Adda[247]

#### [ES - EC - 2009]

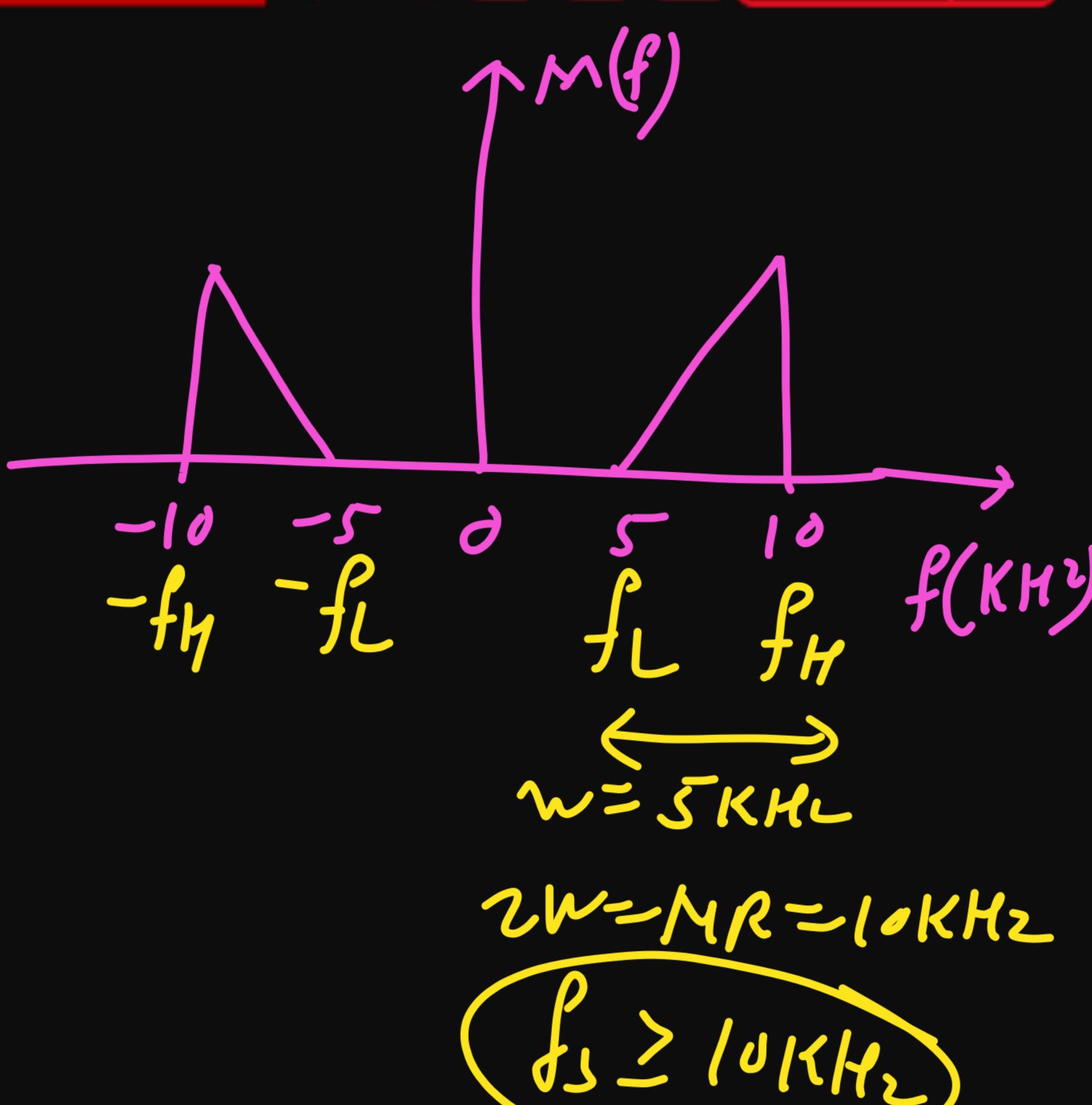

A signal occupies a band 5 kHz to 10 kHz. For proper error free reconstruction at what rate it should be sampled?

(B) 20 kHz

$$\frac{2fL}{2W} = \frac{10}{10} = L = m$$

[GATE - EC - 2007] ) (D.M.)

In delta modulation, the slope overload/ distortion can be reduced by

- (A) decreasing the step size X

- (B) decreasing the granular noise

- (C) decreasing the sampling rate

- (D) increasing the step size

# Adda[24]7

#### [GATE - EC1 - 2015]

A sinusoidal signal of 2 kHz frequency is applied to a delta modulator. The sampling rate and step-size Δ of the delta modulator are 20,000 samples per second and 0.1 V, respectively. To prevent slope overload, the maximum amplitude of the sinusoidal signal (in Volts) is:

$$f_{m} = 2KHZ$$

$$m(t) = A_{m} \sin 2\pi f_{m} + \int_{0}^{\infty} dt dt = A_{m} 2\pi f_{m}$$

$$f_{s} = \frac{1}{T} = 20000 \text{ Simples/sec}$$

$$D = 0.1 \text{ Volt}$$

(C)

$$\frac{2}{\pi}$$

$$\theta_{m} \leq \frac{2000}{2512600} = \frac{1}{25}$$

(B)  $\frac{1}{\pi}$

###

32000

32X1000

#### [GATE - EC - 2006]

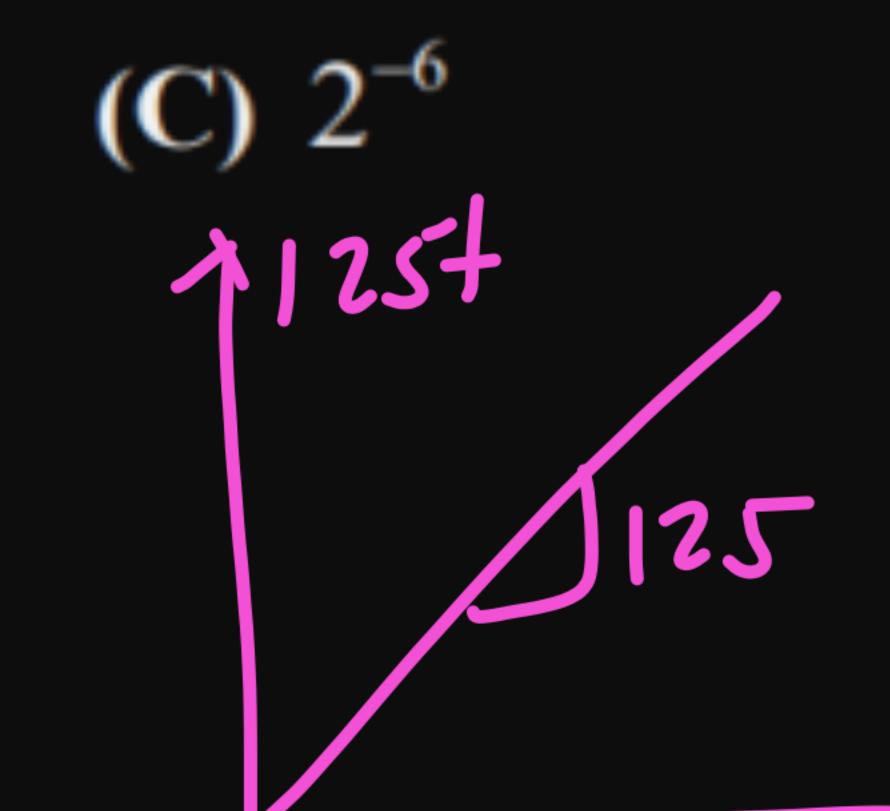

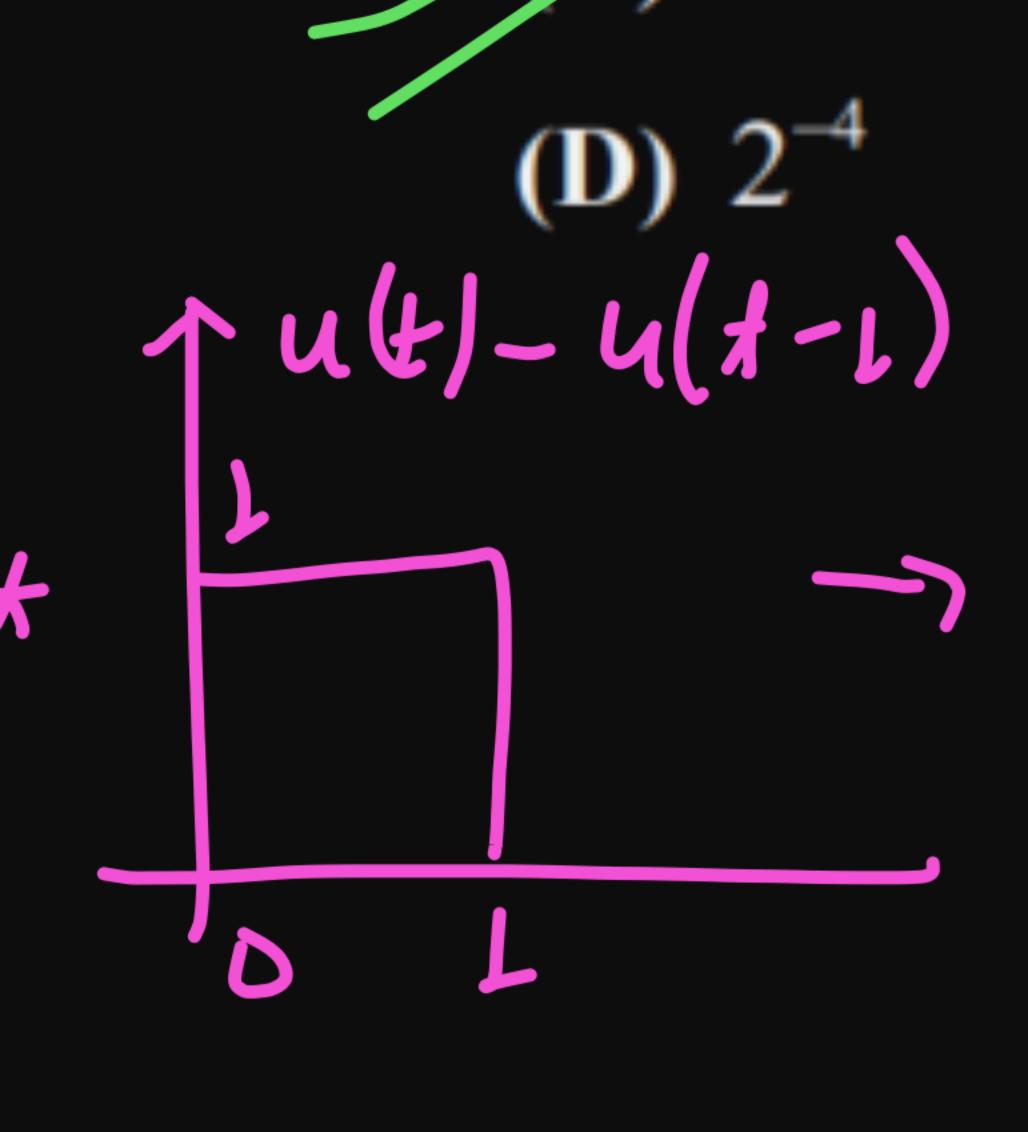

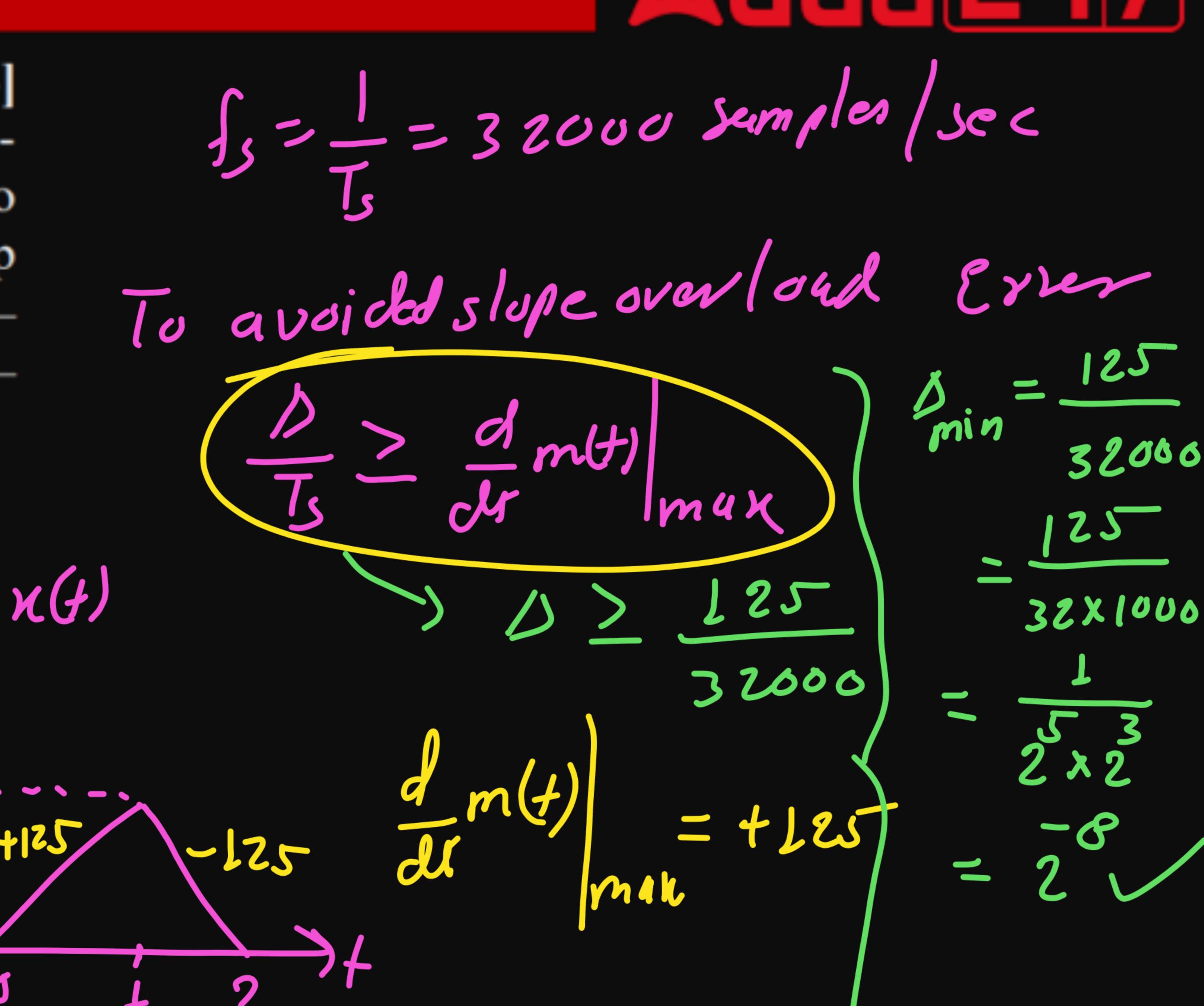

The minimum step-size required for a Delta-Modulator operating at 32K samples/sec to track the signal (here u(t) is the unit-step function) x(t) = 125t(u(t) - u(t - 1)+(250-125t) (u(t - 1)-u(t-2)) so that slope overload is avoided, would be

(A)

$$2^{-10}$$

4125

# Adda 247

[GATE - EC - 2003]

The input to a linear delta modulator having a step size  $\Delta = 0.628$  is a sine wave with frequency  $f_m$  and peak amplitude  $f_m$ . If the sampling frequency  $f_s = 40KHz$ , the combination of the sine-wave frequency and the amplitude, where slope overload will take place is

$D = 0.628, f_s = \frac{1}{4} = 40000$   $m(t) = f_m \sin 2\pi f_m t$   $\int_{Sey}$

To de man

0.628 X 40000 < ZZfm Am

fmam> 0.628× 4000 0.628×400

ZZ

fmAm> 4000)

[ES - EC - 2004]

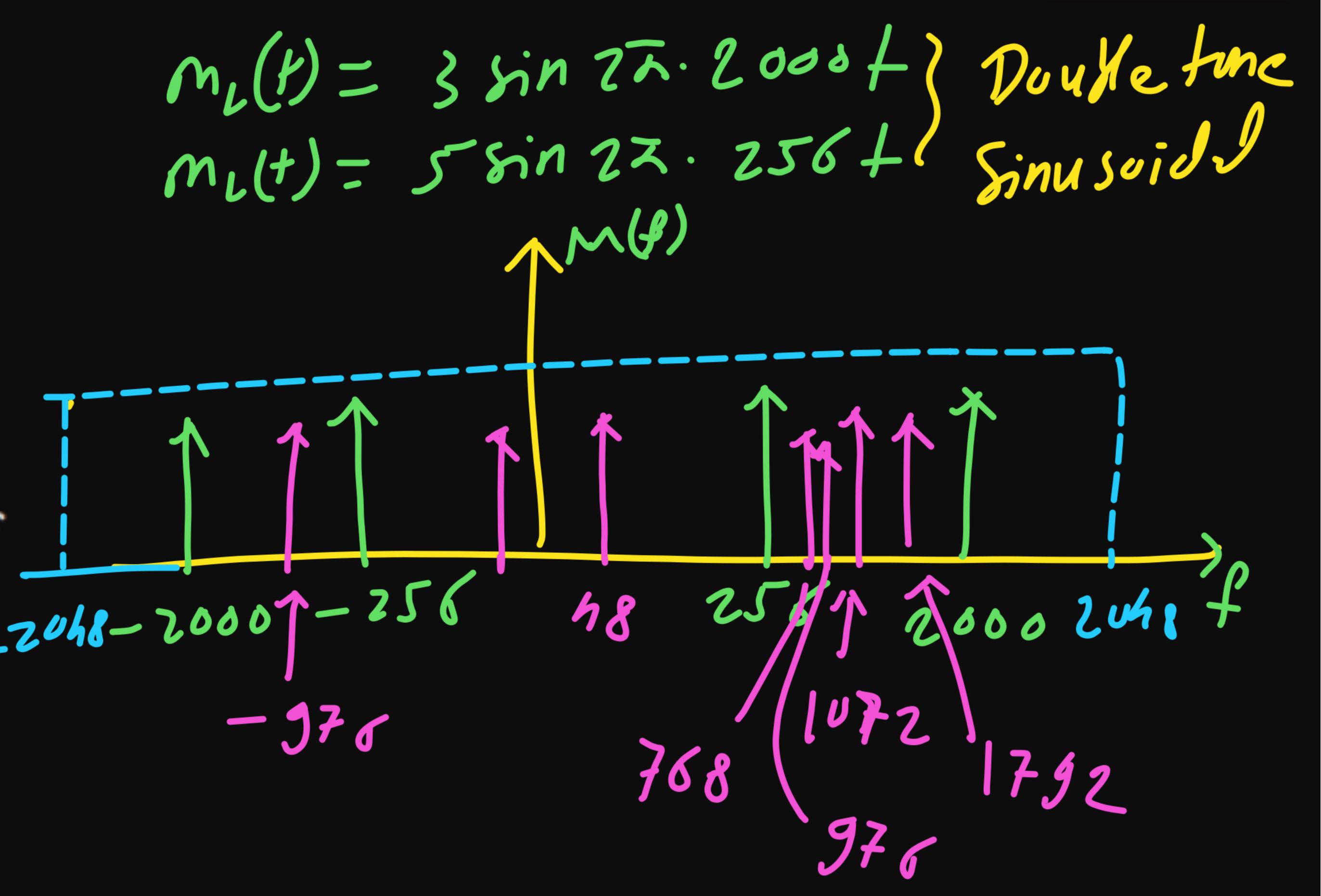

The sum of two signals

$$e_1 = 3\sin(4\pi \times 10^3 t)$$

and  $e_2 = 5\sin(2\pi \times 256t)$

is sampled at 1024 Hz. The sampled signal is passed through a low pass filter with cut-off at 2048 Hz. The output of this filter will 2048 - 2000 - 256 contain components at

- (A) 256 Hz and 10<sup>3</sup> Hz

- (B) 256 Hz and 1024 Hz

- (C) 256 Hz only

- (D) 1024 Hz only

Download Now

Adda 247 APP

THANKS FOR

# Matching Adda 247